April 2011

# FAN7316 LCD Backlight Inverter Drive IC

### **Features**

- High-Efficiency Single-Stage Power Conversion

- Wide Input Voltage Range: 4.5V to 24V

- Backlight Lamp Ballast and Soft Dimming

- Reduces Required External Components

- Precision Voltage Reference Trimmed to 2%

- N-N Half-Bridge Topology

- PWM Control at Fixed Frequency

- Analog and Burst Dimming Function

- Selectable Burst Dimming Polarity by ADIM Voltage

- Striking Frequency Depending on Normal Frequency

- Open-Lamp Protection

- Open-Lamp Regulation

- Short-Circuit Protection

- 20-Pin SOIC

### **Applications**

- LCD TV

- LCD Monitor

### Description

The FAN7316 is a LCD backlight inverter drive IC that controls N-N half-bridge topology. The FAN7316 can also drive push-pull topology.

The FAN7316 provides a low-cost solution by integrating the external open-lamp protection circuit. The operating voltage of the FAN7316 is wide, so the FAN7316 doesn't need an external regulator to supply the voltage to the IC. The FAN7316 has the internal bootstrap driver, so the external fast recovery diode can be avoided.

The FAN7316 provides various protections, such as open-lamp regulation, arc protection, open-lamp protection, short-circuit protection, and CMP-high protection to increase the system reliability. The FAN7316 provides analog dimming, burst dimming, and burst dimming polarity selection functions.

The FAN7316 is available in a 20-SOIC package.

## **Ordering Information**

| Part Number | Package | Operating Temperature | Packing Method |

|-------------|---------|-----------------------|----------------|

| FAN7316MX   | 20-SOIC | -25 to +85°C          | TAPE & REEL    |

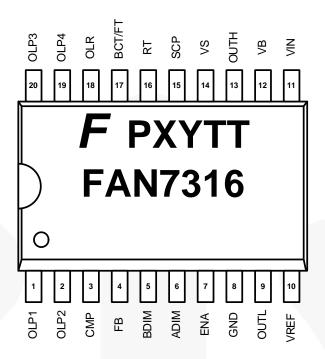

## **Pin Assignments**

F: Fairchild logo

P: Assembly site code

XY: Year & weekly code

TT: Die run code

FAN7316: Device name

Figure 2. Package Diagram

## **Pin Definitions**

| Pin# | Name   | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | OLP1   | This pin is for open-lamp protection. If OLP is lower than 1.5V at initial operation, the IC operates at striking mode for BCT 450 cycles. If OLP is lower than 1.5V in normal mode, the                                                                                                                                                                                                    |  |  |

| 2    | OLP2   | IC is shut down after a delay of three BCT cycles.                                                                                                                                                                                                                                                                                                                                          |  |  |

| 3    | CMP    | Error amplifier output. A compensation capacitor should be connected between this pin and ground.                                                                                                                                                                                                                                                                                           |  |  |

| 4    | FB     | Error amplifier inverting input. This pin voltage is regulated at 2V or ADIM voltage.                                                                                                                                                                                                                                                                                                       |  |  |

| 5    | BDIM   | This pin is for burst dimming input. The voltage range of 0.5 to 2V at this pin controls burst mode duty cycle from 0% to 100%.                                                                                                                                                                                                                                                             |  |  |

| 6    | ADIM   | This pin is for positive analog dimming input. This voltage to 2V at this pin controls the amplitude of the lamp current.                                                                                                                                                                                                                                                                   |  |  |

| 7    | ENA    | This pin is for turning on/off the IC.                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 8    | GND    | Ground.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 9    | OUTL   | Low-side driver output. The output stage can deliver about 500mA source and sink current, typically.                                                                                                                                                                                                                                                                                        |  |  |

| 10   | VREF   | 6V reference voltage.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 11   | VIN    | IC supply voltage.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 12   | VB     | High-side floating supply. The bootstrap capacitor should be connected between this pin and VS pin, which can be fed by an internal bootstrap MOSFET.                                                                                                                                                                                                                                       |  |  |

| 13   | OUTH   | High-side driver output. The output stage can deliver about 500mA source and sink current, typically.                                                                                                                                                                                                                                                                                       |  |  |

| 14   | VS     | High-side floating supply return. Layout care should be taken to avoid below-ground spikes on this pin.                                                                                                                                                                                                                                                                                     |  |  |

| 15   | SCP    | This pin is for short-circuit protection. If SCP is higher than 2V, IC enters shutdown mode after a delay of 32 BCT cycles.                                                                                                                                                                                                                                                                 |  |  |

| 16   | RT     | This pin programs the switching frequency. The resistor should be connected between this pin and ground.                                                                                                                                                                                                                                                                                    |  |  |

| 17   | BCT/FT | This pin programs the burst dimming frequency. A capacitor should be connected between this pin and ground. The waveform of this pin is the triangular waveform whose amplitude is from 0.5V to 2V. This pin voltage goes up to 4V when the IC enters shutdown mode.                                                                                                                        |  |  |

| 18   | OLR    | This pin is for open-lamp regulation. If the voltage at OLR reaches 2V, the IC makes this pin voltage be controlled not to exceed 2V. If OLR voltage is higher than 1.75V, the IC enters shutdown mode after delays of 451 BCT cycles in striking mode and three BCT cycles in normal mode, respectively. If this pin voltage is higher than 3V, the IC enters shutdown mode without delay. |  |  |

| 19   | OLP4   | This pin is for open lamp protection. If OLP is lower than 1.5V at initial operation, the IC                                                                                                                                                                                                                                                                                                |  |  |

| 20   | OLP3   | operates at striking mode for BCT 450 cycles. If OLP is lower than 1.5V in normal mode, the IC is shut down after a delay of three BCT cycles.                                                                                                                                                                                                                                              |  |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                        | Min.              | Max.              | Unit  |

|------------------|--------------------------------------------------|-------------------|-------------------|-------|

| V <sub>IN</sub>  | IC Supply Voltage                                | 4.5               | 24                | V     |

| V <sub>B</sub>   | High-Side Floating Supply                        | -0.3              | 33                | V     |

| Vs               | High-Side Floating Supply Return                 | -2 <sup>(3)</sup> | V <sub>B</sub> -7 | V     |

| $T_J$            | Operating Junction Temperature                   | -40               | +150              | °C    |

| T <sub>STG</sub> | Storage Temperature Range                        | -65               | +150              | °C    |

| $\theta_{JA}$    | Thermal Resistance Junction-Air <sup>(1,2)</sup> |                   | 90                | °C /W |

| P <sub>D</sub>   | Power Dissipation                                |                   | 1.4               | W     |

#### Notes:

- 1. Thermal resistance test board. Size: 76.2mm x 114.3mm x 1.6mm (1S0P); JEDEC standard: JESD51-2, JESD51-3.

- 2. Assume no ambient airflow.

### **Recommended Operating Ratings**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance to the datasheet specifications. Fairchild does not recommend exceeding them or designing to absolute maximum ratings.

| Symbol          | Parameter                        | Min.                | Max.                | Unit |

|-----------------|----------------------------------|---------------------|---------------------|------|

| V <sub>IN</sub> | IC Supply Voltage                | 4.5                 | 22.0                | V    |

| $V_{B}$         | High-Side Floating Supply        | V <sub>S</sub> -0.3 | V <sub>S</sub> +6.5 | V    |

| Vs              | High-Side Floating Supply Return | (3)                 | 25                  | V    |

| $T_A$           | Operating Ambient Temperature    | -25                 | +85                 | °C   |

#### Notes:

3. The V<sub>S</sub> is tolerant to short negative transient spikes.

### Pin Breakdown Voltage

| Pin# | Name | Value | Unit | Pin# | Name   | Value | Unit |

|------|------|-------|------|------|--------|-------|------|

| 1    | OLP1 | 7     |      | 11   | VIN    | 24    |      |

| 2    | OLP2 | 7     |      | 12   | VB     | 33    |      |

| 3    | CMP  | 7     |      | 13   | OUTH   | 7     |      |

| 4    | FB   | 7     |      | 14   | VS     | 33    |      |

| 5    | BDIM | 7     | V    | 15   | SCP    | 7     | V    |

| 6    | ADIM | 7     | V    | 16   | RT     | 7     | V    |

| 7    | ENA  | 7     |      | 17   | BCT/FT | 7     |      |

| 8    | GND  |       |      | 18   | OLR    | 7     |      |

| 9    | OUTL | 7     |      | 19   | OLP4   | 7     |      |

| 10   | VREF | 7     |      | 20   | OLP3   | 7     |      |

### **Electrical Characteristics**

For typical values,  $T_A$ =25°C,  $V_{IN}$ =18V, and -25°C  $\leq T_A \leq$  85°C, unless otherwise specified. Specifications to -25°C  $\sim$  85°C are guaranteed by design based on final characterization results.

| Symbol                   | Parameter                                     | Test Condition                                                           | Min. | Тур. | Max. | Unit   |

|--------------------------|-----------------------------------------------|--------------------------------------------------------------------------|------|------|------|--------|

| V <sub>REF</sub> Section | n (Recommend X7R Capacitor)                   |                                                                          |      |      |      |        |

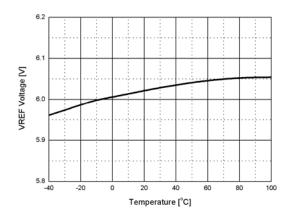

| V <sub>6</sub>           | 6V Regulation Voltage                         | CMP=0V                                                                   | 5.76 | 6.00 | 6.24 | V      |

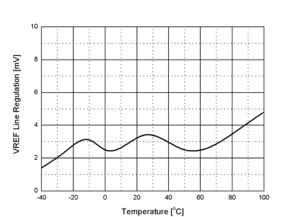

| V <sub>6line</sub>       | 6V Line Regulation                            | V <sub>IN</sub> =7V, 18V                                                 |      |      | 25   | mV     |

| V <sub>6load</sub>       | 6V Load Regulation                            | 10µA≤16≤5mA                                                              |      |      | 60   | mV     |

| Oscillator S             | ection (Main)                                 |                                                                          |      |      |      |        |

| $V_{fbth}$               | FB Threshold Voltage                          | ADIM=1, OLP=0V                                                           |      | 0.45 |      | V      |

| V <sub>cth</sub>         | CT High Voltage <sup>(4)</sup>                |                                                                          |      | 2.0  |      | V      |

| $V_{ctl}$                | CT Low Voltage <sup>(4)</sup>                 |                                                                          |      | 0.5  |      | V      |

| Oscillator S             | ection (Burst)                                |                                                                          |      |      |      | ı      |

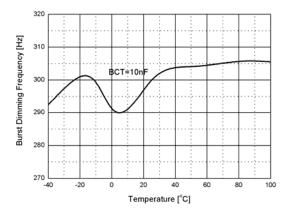

|                          | On all the first Francisco                    | T <sub>A</sub> =25°C, BCT=10nF                                           | 288  | 300  | 312  | Hz     |

| f <sub>oscb</sub>        | Oscillation Frequency                         | BCT=10nF                                                                 | 282  | 300  | 318  | Hz     |

| $V_{bcth}$               | BCT High Voltage                              | BCT=10nF                                                                 |      | 2    |      | V      |

| $V_{bctl}$               | BCT Low Voltage                               | BCT=10nF                                                                 |      | 0.5  |      | V      |

| $V_{\text{bctft}}$       | BCT Fault Voltage                             | SCP=2.5V                                                                 |      | 4    |      | V      |

| Error Ampli              | fier Section                                  |                                                                          | -    |      | •    |        |

| G <sub>m1</sub>          | Error Amplifier Trans-conductance             | CMP=1, ADIM=1V                                                           | 100  | 360  | 600  | umho   |

| A <sub>V</sub>           | Error Amplifier Open-loop Gain <sup>(4)</sup> |                                                                          |      | 50   |      | dB     |

| V2                       | 2V Regulation Voltage                         | T <sub>A</sub> =25°C, ADIM=2.5V                                          | 1.97 | 2.00 | 2.03 | V      |

| ٧Z                       | 2 Vicegulation Voltage                        |                                                                          |      | 260  |      | ppm/°C |

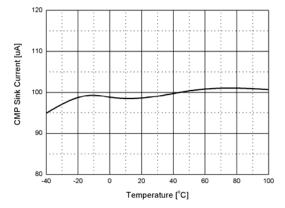

| I <sub>sin</sub>         | CMP Sink Current                              | ADIM=1V, FB=2.5V                                                         | 66   | 100  | 134  | μΑ     |

| I <sub>sur1</sub>        | CMP Source Current 1                          | CMP=1V, FB=0V                                                            | -134 | -100 | -66  | μΑ     |

| I <sub>sur2</sub>        | CMP Source Current 2                          | 1.75V <olr<2v< td=""><td></td><td>1.6</td><td></td><td>μA</td></olr<2v<> |      | 1.6  |      | μA     |

| I <sub>sur3</sub>        | CMP Source Current 3 <sup>(4)</sup>           | OLR>2V                                                                   |      | 0    | /    | μA     |

| Under-Volta              | age Lockout Section (UVLO)                    |                                                                          |      | •    |      | •      |

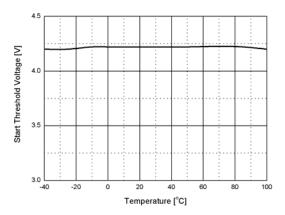

| $V_{th}$                 | Start Threshold Voltage                       | ENA=2.5V                                                                 | 3.9  | 4.2  | 4.5  | V      |

| $V_{thhys}$              | Start Threshold Voltage Hysteresis            | ENA=2.5V                                                                 | 0.2  | 0.4  | 0.6  | V      |

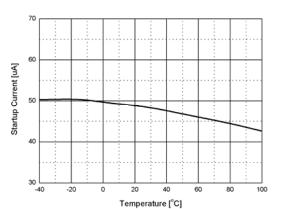

| I <sub>st</sub>          | Start-up Current                              | V <sub>IN</sub> =V <sub>th</sub> -0.2                                    | 20   | 60   | 150  | μA     |

| I <sub>op</sub>          | Operating Supply Current                      | Not switching                                                            |      | 1.5  | 2.0  | mA     |

| ENA Section              | n                                             | •                                                                        |      | •    |      |        |

| V <sub>ena</sub>         | Enable State Input Voltage                    |                                                                          | 2    |      | 5    | V      |

| V <sub>dis</sub>         | Disable Stage Input Voltage                   |                                                                          |      |      | 0.7  | V      |

| I <sub>sb</sub>          | Stand-by Current                              | ENA=0                                                                    |      | 100  | 150  | μA     |

### Note:

4. These parameters, although guaranteed, are not 100% tested in production.

### **Electrical Characteristics** (Continued)

For typical values,  $T_A$ =25°C,  $V_{IN}$ =18V, and -25°C  $\leq T_A \leq$  85°C, unless otherwise specified. Specifications to -25°C  $\sim$  85°C are guaranteed by design based on final characterization results.

| Symbol             | Parameter                                            | Test Condition                        | Min.  | Тур. | Max. | Unit |

|--------------------|------------------------------------------------------|---------------------------------------|-------|------|------|------|

| Protectio          | n Section                                            |                                       |       |      |      |      |

| V <sub>scp</sub>   | Short-Circuit Protection Voltage                     |                                       | 1.9   | 2.0  | 2.1  | V    |

| $V_{cmpr}$         | CMP Protection Voltage                               |                                       | 2.8   | 3.0  | 3.2  | V    |

| V <sub>olp</sub>   | Open-Lamp Protection Voltage                         |                                       | 1.4   | 1.5  | 1.6  | V    |

| V <sub>ovp</sub>   | Over-Voltage Protection                              |                                       | 2.85  | 3.00 | 3.15 | V    |

| V <sub>olr1</sub>  | Open-Lamp Regulation Voltage 1                       |                                       | 1.60  | 1.75 | 1.90 | V    |

| V <sub>olr2</sub>  | Open-Lamp Regulation Voltage 2                       |                                       | 1.9   | 2.0  | 2.1  | V    |

| $V_{olrhy}$        | Open-Lamp Regulation Hysteresis <sup>(5)</sup>       |                                       |       | 250  |      | mV   |

| 1                  | Chart Circuit Dratactics Dalou(5)                    | Striking, f <sub>oscb</sub> =300Hz    | 1.4   | 1.5  | 1.6  | S    |

| t <sub>scp</sub>   | Short-Circuit Protection Delay <sup>(5)</sup>        | Normal, f <sub>oscb</sub> =300Hz      | 80    | 100  | 120  | ms   |

| . /                | CMD Destantion Delay (5)                             | Striking, f <sub>oscb</sub> =300Hz    | 1.4   | 1.5  | 1.6  | S    |

| t <sub>cmp</sub>   | CMP Protection Delay <sup>(5)</sup>                  | Normal, f <sub>oscb</sub> =300Hz      | 80    | 100  | 120  | ms   |

| . /                | C   D   (5)                                          | Striking, f <sub>oscb</sub> =300Hz    | 1.4   | 1.5  | 1.6  | S    |

| t <sub>olp</sub>   | Open-Lamp Protection Delay <sup>(5)</sup>            | Normal, f <sub>oscb</sub> =300Hz      | 6     |      | 10   | ms   |

|                    | Open Lemp Regulation Polov <sup>(5)</sup>            | Striking, f <sub>oscb</sub> =300Hz    | 1.4   | 1.5  | 1.6  | S    |

| t <sub>olr</sub>   | Open-Lamp Regulation Delay <sup>(5)</sup>            | Normal, f <sub>oscb</sub> =300Hz      | 80    | 100  | 120  | ms   |

| TSD                | Thermal Shutdown <sup>(5)</sup>                      |                                       | 1     | 150  |      | °C   |

| Output S           | ection                                               |                                       | ,     |      | •    |      |

|                    |                                                      | $T_A=25$ °C, $R_T=27$ k $\Omega$      | 47.4  | 49.0 | 50.6 | kHz  |

| f <sub>nrmo</sub>  | Output Normal Frequency                              | $R_T=27k\Omega$                       | 47    | 49   | 51   |      |

|                    |                                                      | $T_A=25$ °C, $R_T=27$ k $\Omega$      | 61.5  | 64.0 | 66.4 |      |

| f <sub>str</sub>   | Output Striking Frequency                            | $R_T=27k\Omega$                       | 61    | 64   | 67   | kHz  |

| V <sub>ouvh</sub>  | OUTH Voltage Before Start-up                         | V <sub>IN</sub> =V <sub>th</sub> -0.6 | -0.45 | 0    | 0.45 | V    |

| V <sub>ouvl</sub>  | OUTL Voltage Before Start-up                         | V <sub>IN</sub> =V <sub>th</sub> -0.6 | -0.45 | 0    | 0.45 | V    |

| V <sub>osth</sub>  | High-Side Output Voltage at V <sub>ENA</sub> =0V     | V <sub>IN</sub> =18V                  | -0.45 | 0    | 0.45 | V    |

| V <sub>ost</sub>   | Low-Side Output Voltage at V <sub>ENA</sub> =0V      | V <sub>IN</sub> =18V                  | -0.45 | 0    | 0.45 | V    |

| V <sub>ohh</sub>   | High-Side Output Voltage                             | V <sub>IN</sub> =18V                  | 5.5   | 6.0  | 6.5  | V    |

| V <sub>ohl</sub>   | Low-Side Output Voltage                              | V <sub>IN</sub> =18V                  | 5.5   | 6.0  | 6.5  | V    |

| I <sub>dsurh</sub> | High-Side Output Drive Source Current <sup>(5)</sup> | V <sub>IN</sub> =18V                  |       | 500  |      | mA   |

| I <sub>dsinh</sub> | High-Side Output Drive Sink Current <sup>(5)</sup>   | V <sub>IN</sub> =18V                  |       | 500  |      | mA   |

| I <sub>dsurl</sub> | Low-Side Output Drive Source Current <sup>(5)</sup>  | V <sub>IN</sub> =18V                  |       | 500  | /-   | mA   |

| I <sub>dsinI</sub> | Low-Side Output Drive Sink Current <sup>(5)</sup>    | V <sub>IN</sub> =18V                  |       | 500  |      | mA   |

| t <sub>dead</sub>  | Dead Time <sup>(5)</sup>                             |                                       |       | 500  |      | ns   |

| Noto:              |                                                      |                                       | ı     | 1    | L    |      |

### Note:

5. These parameters, although guaranteed, are not 100% tested in production.

## **Typical Performance Characteristics**

Figure 3. Start Threshold Voltage vs. Temp.

Figure 5. Start-up Current vs. Temp.

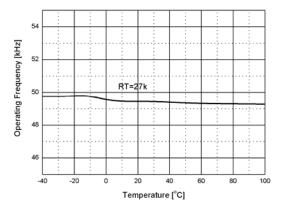

Figure 7. Operating Frequency vs. Temp.

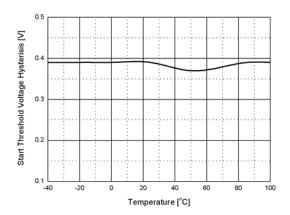

Figure 4. Start Threshold Voltage Hys. vs. Temp.

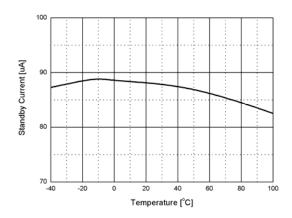

Figure 6. Standby Current vs. Temp.

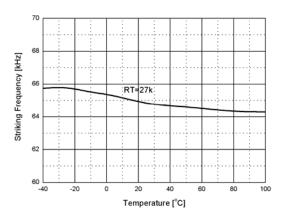

Figure 8. Striking Frequency vs. Temp.

## **Typical Performance Characteristics** (Continued)

Figure 9. Burst Dimming Frequency vs. Temp.

Figure 11. V<sub>REF</sub> Line Regulation Voltage vs. Temp.

Figure 13. CMP Sink Current vs. Temp.

Figure 10.  $V_{REF}$  Voltage vs. Temp.

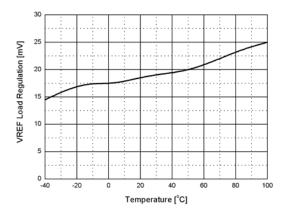

Figure 12. V<sub>REF</sub> Load Regulation Voltage vs. Temp.

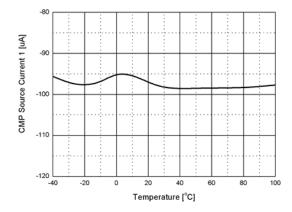

Figure 14. CMP Source Current 1 vs. Temp.

## **Typical Performance Characteristics** (Continued)

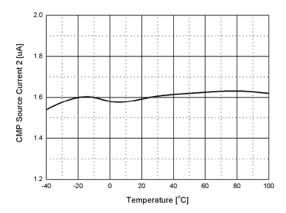

Figure 15. CMP Source Current 2 vs. Temp.

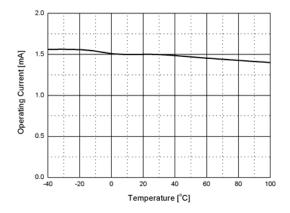

Figure 16. Operating Current vs. Temp.

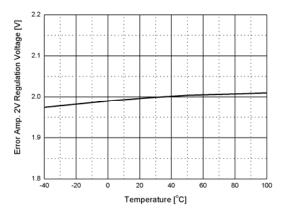

Figure 17. Error Amplifier 2V Voltage vs. Temp.

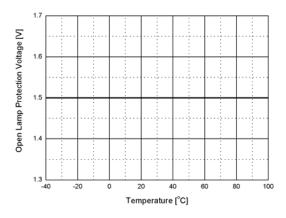

Figure 18. Open-Lamp Protection Voltage vs. Temp.

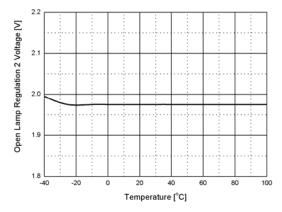

Figure 19. Open-Lamp Regulation Voltage 2 vs. Temp.

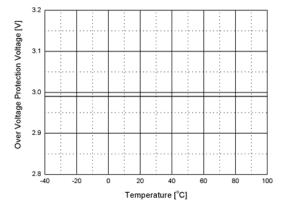

Figure 20. Over-Voltage Protection vs. Temp.

## **Typical Performance Characteristics** (Continued)

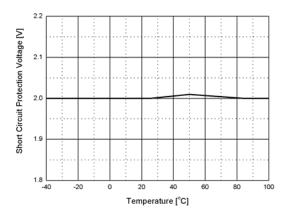

Figure 21. Short-Circuit Protection Voltage vs. Temp.

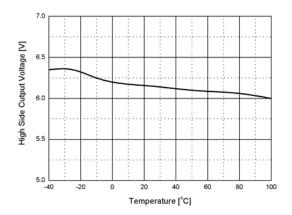

Figure 22. High-Side Output Voltage vs. Temp.

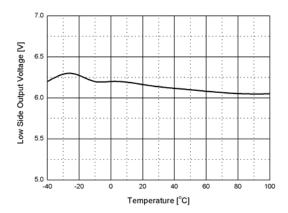

Figure 23. Low-Side Output Voltage vs. Temp.

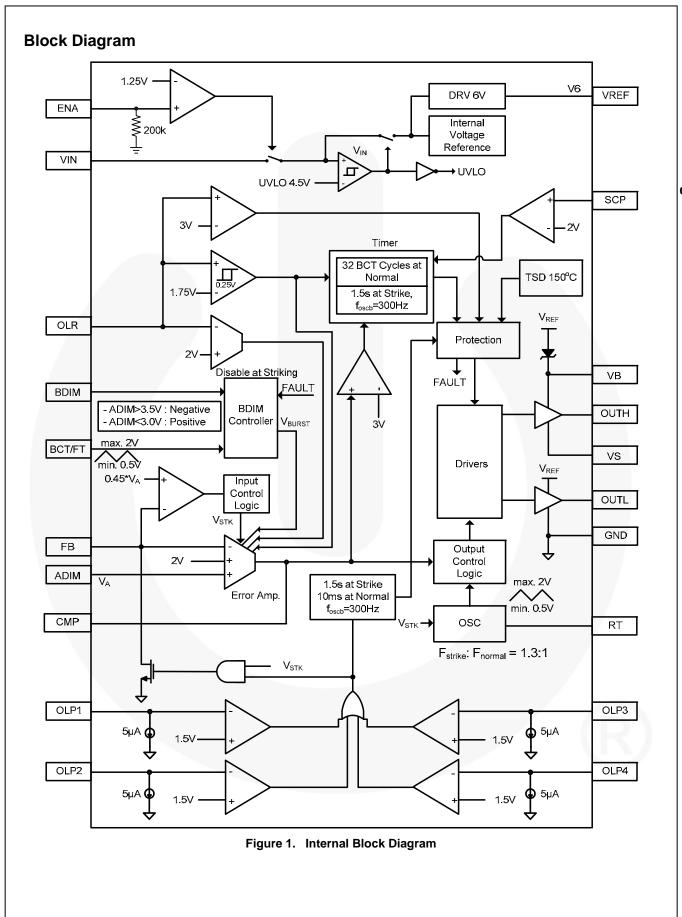

### **Functional Description**

**UVLO:** The under-voltage lockout (UVLO) circuit guarantees the stable operation of the IC's control circuit by stopping and starting it as a function of the  $V_{\rm IN}$  value. The UVLO circuit turns on the control circuit when  $V_{\rm IN}$  exceeds 4.5V. When  $V_{\rm IN}$  is lower than 3.9V, the IC's startup current is less than 150µA.

**ENA:** Applying voltage higher than 2V to the ENA pin enables the IC. Applying voltage lower than 0.7V to the ENA pin disables the IC.

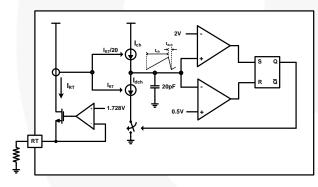

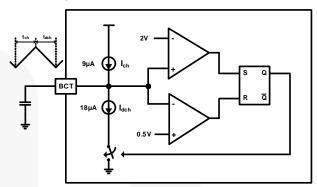

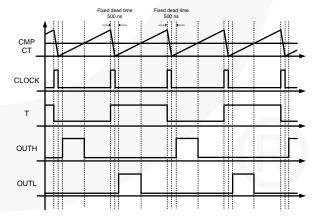

Internal Main Oscillator: The internal timing capacitor (CT), 20pF, is charged by the reference current source, which is formed by the timing resistor (RT). The RT voltage is regulated at 1.728V. The sawtooth waveform charges up to 2V. Once CT voltage is reached, the CT begins discharging down to 0.5V. Next, the CT starts charging again and a new switching cycle begins, as shown in Figure 24. The main frequency is programmed by adjusting the  $R_{\rm T}$  value. The main frequency is calculated as:

$$f_{OSC} \approx \frac{2736}{R_T[K\Omega]}[KHz]$$

(1)

Figure 24. Main Oscillator Circuit

The striking frequency is 1.3 times as high as the main frequency.

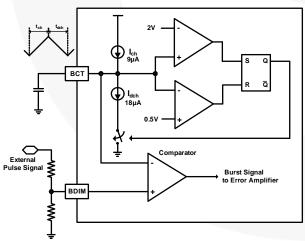

**Burst Dimming Oscillator:** The burst capacitor timing (BCT) is charged by the internal reference current source. The triangular waveform charges up to 2V. Once the BCT voltage is reached, the capacitor begins discharging down to 0.5V. Next, the BCT starts charging again and a new switching cycle begins, as shown in Figure 25. The burst dimming frequency is programmed by adjusting BCT value. The burst dimming frequency is calculated as:

$$f_{OSCB} \approx \frac{3 \cdot 10^3}{BCT[nF]}[Hz]$$

(2)

To avoid visible flicker, the burst dimming frequency should be greater than 120Hz.

Figure 25. Burst Dimming Oscillator Circuit

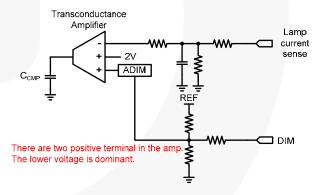

**Analog Dimming:** There are two kinds of analog dimming polarity: positive analog dimming and negative analog dimming.

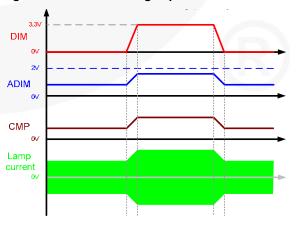

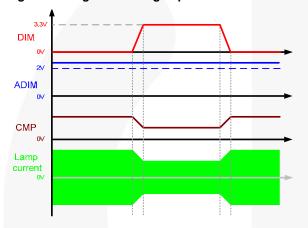

For positive analog dimming, the lamp intensity is controlled with the ADIM signal. The lamp intensity is proportional to ADIM signal; as ADIM voltage increases, the lamp intensity increases. Figure 26 shows how to implement negative analog dimming circuit and Figure 27 shows the lamp current waveform vs. DIM in positive analog dimming mode.

Figure 26. Positive Analog Implementation Circuit

#### Figure 27. Positive Analog Dimming Waveform

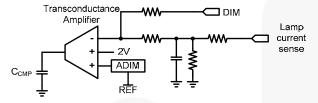

For negative analog dimming, the lamp intensity is controlled with the external DIM signal and the resistors. The lamp intensity is inversely proportional to DIM voltage. As DIM voltage increases, the lamp intensity decreases. Figure 28 shows how to implement a negative analog dimming circuit and Figure 29 shows the lamp current waveform vs. DIM in negative analog dimming mode.

Figure 28. Negative Analog Implementation Circuit

Figure 29. Negative Analog Dimming Waveform

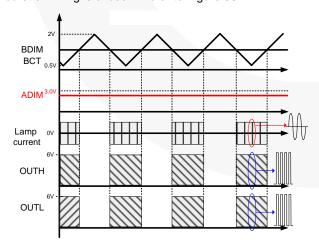

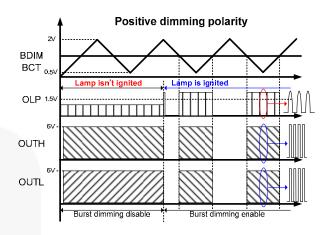

**Burst Dimming Polarity Selection:** FAN7316 provides the function to select burst dimming polarity by ADIM pin voltages. If ADIM pin voltage is lower than 3V, positive burst dimming is chosen. Refer to Figure 30.

Figure 30. Positive Burst Dimming Chosen

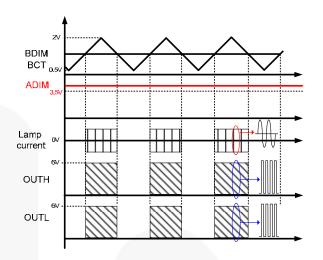

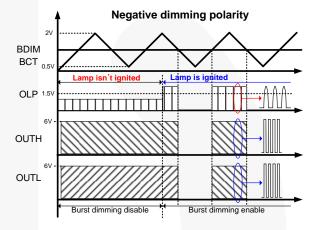

If the ADIM pin voltage is higher than 3.5V, negative dimming polarity is chosen. Refer to Figure 31.

Figure 31. Negative Burst Dimming Chosen

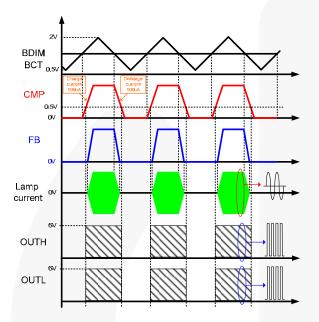

**Burst Dimming:** There are also two kinds of burst dimming polarity: positive analog dimming and negative analog dimming. The lamp intensity is controlled with the BDIM voltage. By comparing the BDIM voltage with the 0.5~2V triangular waveform of burst dimming oscillator (BCT), the PWM pulse is generated. The PWM pulse controls the CMP voltage by discharging and charging the CMP capacitor.

For positive burst dimming, when BDIM voltage is higher than BCT voltage, the lamp current is turned on. So, 2V on BDIM commands full brightness. The duty cycle of the PWM pulse determines the lamp brightness. The lamp intensity is proportional to BDIM voltage. As BDIM voltage increases, the lamp intensity also increases. Figure 32 shows the lamp current waveform vs. DIM in positive analog dimming mode.

Figure 32. Positive Burst Dimming Operation

For negative burst dimming, when BDIM voltage is lower than BCT voltage, the lamp current is turned on. So, 0V on BDIM commands full brightness. The duty cycle of the PWM pulse determines the lamp brightness. The lamp intensity is inversely proportional to BDIM voltage. As BDIM voltage increases, the lamp intensity decreases. Figure 32 shows the lamp current waveform vs. DIM in negative analog dimming mode.

Figure 33. Positive Burst Dimming Operation

Burst dimming can be implemented by not only DC voltage, also PWM pulse as BDIM signal. Figure 34 shows how to implement burst dimming by using PWM pulse as BDIM signal.

Figure 34. Burst Dimming Using an External Pulse

During striking mode, burst dimming operation is disabled to guarantee the continuous striking time. Figure 35 shows that burst dimming is disabled during striking mode.

Figure 35. Burst Dimming During Striking Mode

**Output Drives:** FAN7316 is designed to drive high-side and low-side MOSFETs with symmetrical duty cycle. A fixed dead time of 500ns is introduced between two outputs at maximum duty cycle, as shown Figure 36.

Figure 36. MOSFETs Gate Drive Signal

**Bootstrap Operation:** To choose the proper  $C_{\text{BS}}$  value, the external MOSFET can be seen as an equivalent capacitor. This capacitor,  $C_{\text{IN}}$ , is related to the MOSFET total gate charge as:

$$C_{IN} = \frac{Q_{GATE}}{V_{GATE}}$$

(3)

The ratio between capacitors  $C_{\text{IN}}$  and  $C_{\text{BS}}$  is proportional to the cyclical voltage loss:

$$C_{BS} >> C_{IN} \tag{4}$$

For example: if  $Q_{GATE}$  is 24nC and  $V_{GATE}$  is 10V,  $C_{IN}$  is 2.4nF. With  $C_{BS}$ =100nF, the drop is 240mV.

The bootstrap driver introduces a voltage drop due to MOSFET  $R_{DSON}$  (typical value:  $100\Omega$ ). The following equation is useful to compute the voltage drop on the bootstrap MOSFET:

$$V_{DROP} = I_{CHARGE} \bullet R_{DSON} \rightarrow V_{DROP} = \frac{Q_{GATE}}{T_{CHARGE}} \bullet R_{DSON}$$

(5)

where  $Q_{\text{GATE}}$  is the gate charge of the external MOSFET,  $R_{\text{DSON}}$  is the on resistance of the bootstrap MOSFET, and  $T_{\text{CHARGE}}$  is the charging time of the bootstrap capacitor.

For example: If  $Q_{\text{GATE}}$  is 24nC and  $T_{\text{CHARGE}}$  is 10 $\mu$ s, the drop on the bootstrap MOSFET is about 0.24V.

$$V_{DROP} = \frac{24nC}{10\mu s} \bullet 100\Omega = 0.24V$$

(6)

**Protections:** The FAN7316 has several protections: Open-Lamp Regulation (OLR), Arc Protection, Open-Lamp Protection (OLP), Short-Circuit Protection (SCP), CMP-High Protection, and Thermal Shutdown (TSD). All protections are latch-mode protections. The latch is reset when  $V_{\text{IN}}$  falls to the UVLO voltage or ENA is pulled down to GND.

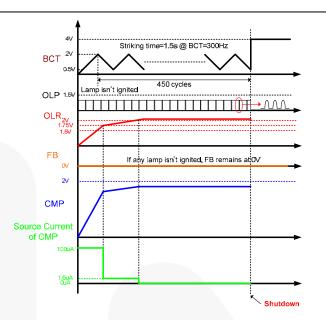

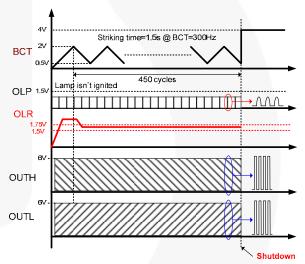

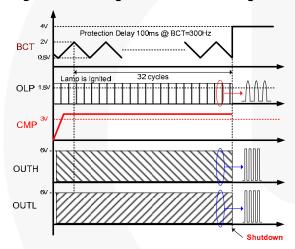

**Open-Lamp Regulation:** When a voltage higher than 2V is applied to the OLR pin, the IC enters regulation mode and controls CMP voltage. The IC limits the lamp voltage by decreasing CMP source current. If the OLR voltage is higher than 1.75V, CMP source current decreases from 100μA to 1.6μA. If the OLR voltage reaches at 2V, CMP source current decreases to 0μA, so CMP voltage remains constant and the lamp voltage also remains constant, as shown in Figure 37. At the same time, the counter based on BCT time starts counting 450 cycles and 32 cycles at striking mode and normal mode, respectively, then the IC enters shutdown, as shown in Figure 38 and Figure 39.

Figure 37. Open-Lamp Regulation in Striking Mode

Figure 38. Open-Lamp Regulation in Striking Mode

Figure 39. Open-Lamp Regulation in Normal Mode

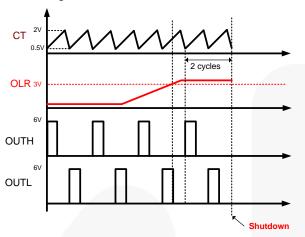

**Arc Protection:** If OLR voltage is higher than 3V, the IC enters shutdown mode after a delay of two CT cycles, as shown in Figure 40.

Figure 40. Arc Protection

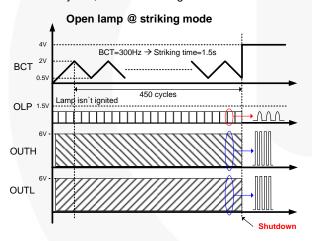

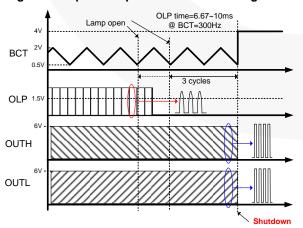

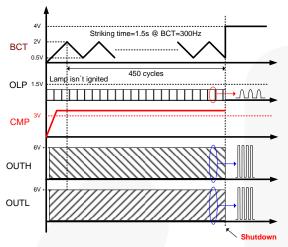

**Open-Lamp Protection:** If OLP is lower than 1.5V at initial operation, the IC operates at striking mode for BCT 450 cycles, as shown in Figure 41. If OLP is lower than 1.5V at normal mode, the IC is shut down after a delay of three BCT cycles, as shown in Figure 42.

Figure 41. Open-Lamp Protection in Striking Mode

Figure 42. Open-Lamp Protection in Normal Mode

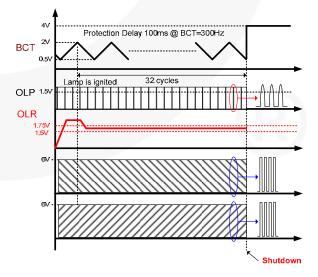

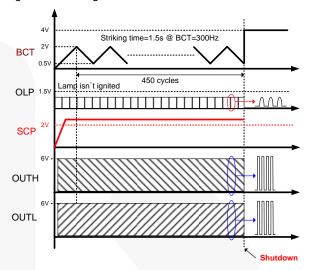

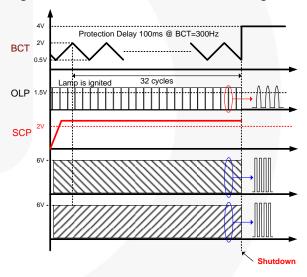

**Short-Circuit Protection:** If SCP is higher than 2V, the counter based on BCT time starts counting 450 cycles and 32 cycles at striking mode and normal mode, respectively, then the IC enters shutdown, as shown in Figure 43 and Figure 44.

Figure 43. Short-Circuit Protection in Striking Mode

Figure 44. Short-Circuit Protection in Normal Mode

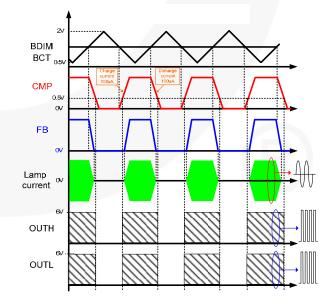

**CMP-High Protection:** If CMP is higher than 3V, the counter based on BCT time starts counting 450 cycles and 32 cycles at striking mode and normal mode, respectively, then the IC enters shutdown, as shown in Figure 45 and Figure 46.

**CMP-High Protection:** If CMP is higher than 3V, the counter based on BCT time starts counting 450 cycles and 32 cycles at striking mode and normal mode, respectively, then the IC enters shutdown, as shown in Figure 45 and Figure 46.

Figure 45. CMP-High Protection in Striking Mode

Figure 46. CMP-High Protection in Normal Mode

**Thermal Shutdown:** The IC provides the function to detect the abnormal over-temperature. If the IC temperature exceeds approximately 150°C, the thermal shutdown triggers.

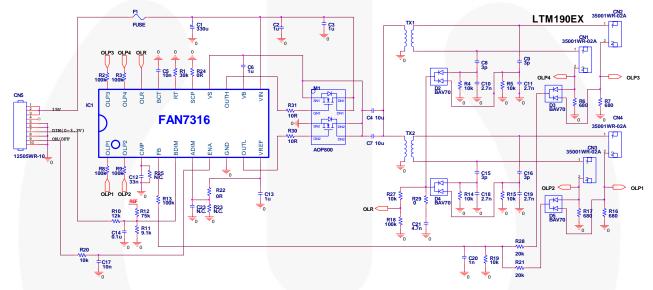

## **Typical Application Circuit (LCD Backlight Inverter)**

| Application         | Device  | Input Voltage Range | Number of Lamps |

|---------------------|---------|---------------------|-----------------|

| 19-Inch LCD Monitor | FAN7316 | 14.5±10%            | 4               |

### 1. Features

- High-Efficiency Single-Stage Power Conversion

- N-N Half-Bridge Topology

- Reduces Required External Components

- Enhanced System Reliability through Protection Functions

Figure 47. Typical Application Circuit

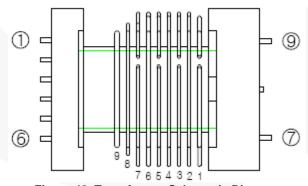

### 2. Transformer Schematic Diagram

Figure 48. Transformer Schematic Diagram

### 3. Core & Bobbin

Core: EFD2126Material: PL7Bobbin: EFD2126

## 4. Winding Specification

| Pin No.      | Wire        | Turns          | Inductance | Leakage Inductance | Remarks  |

|--------------|-------------|----------------|------------|--------------------|----------|

| 5 → 2        | 1 UEW 0.45φ | 12             | 94µH       | 9.1µH              | 1kHz, 1V |

| 7 <b>→</b> 9 | 1 UEW 0.04φ | 2560(=0+360•7) | 3.88H      | 420mH              | 1kHz, 1V |

## 5. BOM of the Application Circuit

| Part Ref.       | Value        | Description | Part Ref. | Value        | Description             |

|-----------------|--------------|-------------|-----------|--------------|-------------------------|

|                 | Fuse         |             | C5        | 10nF         | 50V 1608 K              |

| F1              | 24V 3A       | FUSE        | C6        | 1μF          | 50V 2012 K              |

|                 | Resistor (SN | MD)         | C7        | 10μF         | 16V 3216                |

| R1              | 30k          | 1608 F      | C10       | 2.7nF        | 50V 1608 K              |

| R2              | 100k         | 1608 J      | C11       | 2.7nF        | 50V 1608 K              |

| R3              | 100k         | 1608 J      | C12       | 33nF         | 50V 1608 K              |

| R4              | 10k          | 1608 F      | C13       | 1μF          | 50V 3216 K              |

| R5              | 10k          | 1608 F      | C14       | 10nF         | 50V 1608 K              |

| R6              | 680          | 1608 F      | C17       | 10nF         | 50V 1608 K              |

| R7              | 680          | 1608 F      | C18       | 2.7nF        | 50V 1608 K              |

| R8              | 100k         | 1608 J      | C19       | 2.7nF        | 50V 1608 K              |

| R9              | 100k         | 1608 J      | C20       | 1nF          | 50V 1608 K              |

| R10             | 12k          | 1608 F      | C21       | 4.7nF        | 50V 1608 K              |

| R11             | 9.1k         | 1608 F      | C23       | NC           |                         |

| R12             | 75k          | 1608 F      |           | Capacito     | or (DIP)                |

| R13             | 100k         | 1608 J      | C8        | 3р           | 3KV                     |

| R14             | 10k          | 1608 F      | C9        | 3р           | 3KV                     |

| R15             | 10k          | 1608 F      | C15       | 3р           | 3KV                     |

| R16             | 680          | 1608 F      | C16       | 3р           | 3KV                     |

| R17             | 680          | 1608 F      |           | Diode (      | SMD)                    |

| R18             | 100k         | 1608 F      | D2        | BAV70        | Fairchild Semiconductor |

| R19             | 10k          | 1608 F      | D3        | BAV70        | Fairchild Semiconductor |

| R20             | 10k          | 1608 J      | D4        | BAV70        | Fairchild Semiconductor |

| R21             | 20k          | 1608 F      | D5        | BAV70        | Fairchild Semiconductor |

| R22             | 0            |             |           | Electrolytic | capacitor               |

| R23             | NC           |             | C1        | 330µ         | 25V                     |

| R24             | 0            |             |           | MOSFET       | (SMD)                   |

| R25             | NC           |             | M1        | AOP800       | Alpha & Omega           |

| R27             | 10k          | 1608 F      |           | Wafer (      | SMD)                    |

| R28             | 20k          | 1608 F      | CN1       | 35001WR-02A  |                         |

| R29             | 0            |             | CN2       | 35001WR-02A  |                         |

| R30             | 10           | 1608 J      | CN3       | 35001WR-02A  |                         |

| R31             | 10           | 1608 J      | CN4       | 35001WR-02A  |                         |

| Capacitor (SMD) |              |             | CN5       | 12505WR-10   |                         |

| C2              | 1µF          | 50V 3216 K  |           | Transform    | ner (DIP)               |

| C3              | 1μF          | 50V 3216 K  | TX1       |              | EFD2126                 |

| C4              | 10µF         | 16V 3216    | TX2       |              | EFD2126                 |

### **Physical Dimensions** 13.00 12.60 11.43 В 9.50 10.65 7.60 10.00 7.40 10 1.27 1.27 PIN ONE INDICATOR 0.35 ⊕ 0.25 M C B A LAND PATTERN RECOMMENDATION 2.65 MAX SEE DETAIL A 0.33 0.20 △ 0.10 C 0.30 0.10 **SEATING PLANE** NOTES: UNLESS OTHERWISE SPECIFIED (R0.10) A) THIS PACKAGE CONFORMS TO JEDEC **GAGE PLANE** MS-013, VARIATION AC, ISSUE E (R0.10)B) ALL DIMENSIONS ARE IN MILLIMETERS. 0.25 C) DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS. D) CONFORMS TO ASME Y14.5M-1994 1.27 SEATING PLANE E) LANDPATTERN STANDARD: SOIC127P1030X265-20L -(1.40) F) DRAWING FILENAME: MKT-M20BREV3 **DETAIL A**

Figure 49. 20-SOIC Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

EPSTM AccuPower™ F-PFST Auto-SPM™ FRFET® AX-CAPTM Global Power ResourcesM BitSiC® Green FPS™ Build it Now™ Green FPS™ e-Series™ CorePLUST\*\* CorePOWER\*\* Gmax™. CROSSVOLT™ GTO™ IntelliMAX\*\* CTITM ISOPLANAR™ Current Transfer Logic™ DEUXPEED<sup>®</sup> MegaBuck™ Dual Cool™ MICROCOUPLERTM EcoSPARK® MicroFET\*\* EfficientMax™ MicroPak™ ESBC™ **F**® MicroPak2™ Miller DriveTM MotionMax™ Fairchild® Motion-SPM™ Fairchild Semiconductor® mVVSaver\* FACT Quiet Series™ OptoHiT\*\*

Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™ QFÉT<sup>®</sup>

QSTM Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™ SignalWise™

SMART START™ SPM® STEALTH™ SuperFET® SuperSOT\*\*3 SuperSOT\*\*-8 SuperSOT\*\*-8 SupreMOS® SyncFET™ Sync-Lack™

SmartMax™

The Power Franchise® The Right Technology for Your Success™

wer franchise TinyBoost™ TinyBuck<sup>™</sup> TinyCalc™ TinyLogic® TINY OPTOT TinvPower\*\* TinyPWM™

TinyWire™ TranSiC® TriFault Detect™ TRUECURRENT®\* μSerDes™

UHC Ultra FRFE™ **UniFET™** VCXTM VisualMax™ XS™

#### DISCLAIMER

FACT

FAST®

FastvCore™

FETBench™

FlashVVriter®\*

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN, NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION

#### As used herein

Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user

OPTOLOGIC®

PDP SPM™

OPTOPLANAR®

2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy, Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support.

Counterfeiting of serriconductor parts is a growing problem in the industry. All manufacturers of serriconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Datasheet Identification | Product Status           | Definition                                                                                                                                                                                          |

|--------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information      | Formative /<br>In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary              | First Production         | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed | Full Production          | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete                 | Not In Production        | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev. 154

<sup>\*</sup> Trademarks of System General Corporation, used under license by Fairchild Semiconductor.